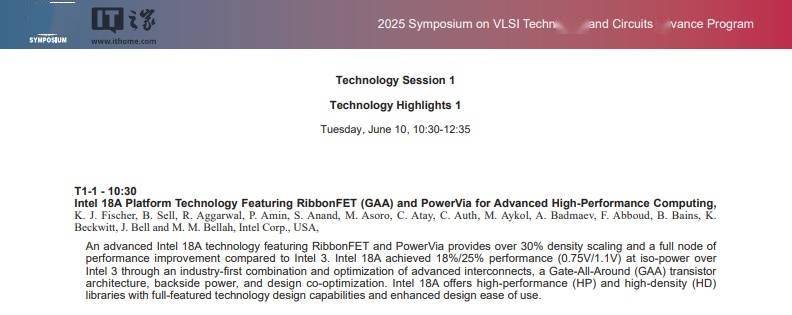

在半導(dǎo)體行業(yè)的矚目之下,2025年超大規(guī)模集成電路研討會(VLSI Symposium)即將于6月8日至12日在日本京都拉開帷幕。作為該領(lǐng)域最負盛名的國際盛會,VLSI Symposium每年都會吸引全球頂尖企業(yè)和學(xué)者共襄盛舉。

近日,VLSI官方提前發(fā)布了一系列即將在研討會上揭曉的論文預(yù)覽,其中Intel的18A工藝技術(shù)細節(jié)尤為引人注目。據(jù)悉,相較于Intel 3制程,18A節(jié)點在性能、能耗及面積(PPA)三大關(guān)鍵指標(biāo)上均實現(xiàn)了顯著提升,有望為消費級客戶端產(chǎn)品及數(shù)據(jù)中心產(chǎn)品帶來革命性的進步。

據(jù)英特爾透露,在相同電壓(1.1V)和復(fù)雜度條件下,18A制程可使標(biāo)準(zhǔn)Arm核心子模塊的性能提升25%;而在保持相同頻率和電壓的情況下,其功耗較Intel 3降低了36%。更令人驚嘆的是,在低壓狀態(tài)(0.75V)下,18A制程不僅實現(xiàn)了18%的性能提升,還同時降低了38%的功耗。該工藝相較于Intel 3實現(xiàn)了0.72的面積微縮,進一步提升了芯片的整體效率。

18A制程之所以能夠?qū)崿F(xiàn)如此顯著的PPA優(yōu)勢,得益于其采用的全環(huán)繞柵極(GAA)RibbonFET晶體管與PowerVia背面供電網(wǎng)絡(luò)(BSPDN)兩大核心技術(shù)。這兩項技術(shù)的結(jié)合,不僅提升了晶體管的密度和面積效率,還優(yōu)化了柵極、源漏極及接觸結(jié)構(gòu),從而提高了單元集成密度與均質(zhì)性。

在具體應(yīng)用方面,18A工藝的高性能(HP)庫單元高度從240CH降至180CH,高密度(HD)庫從210CH縮減至160CH,垂直尺寸平均縮減約25%。這意味著在相同面積內(nèi)可以容納更多的晶體管,從而大幅提升芯片的性能和能效。

PowerVia技術(shù)通過將供電線路轉(zhuǎn)移至芯片背面,釋放了正面的信號布線空間,進一步提升了芯片的集成度和信號傳輸質(zhì)量。這些技術(shù)改進使得18A制程在單位面積性能與能效表現(xiàn)上取得了突破性的進展,為先進芯片設(shè)計提供了強有力的支持。

在量產(chǎn)方面,英特爾計劃在今年晚些時候啟動Panther Lake處理器的量產(chǎn)工作,而數(shù)據(jù)中心芯片Clearwater Forest則預(yù)計將于2026年初實現(xiàn)量產(chǎn)。首款基于18A工藝的第三方芯片設(shè)計也預(yù)計將在2025年中期完成流片驗證。

蘋果、英偉達、英特爾以及Alphawave Semi的工程師共同署名了一篇關(guān)于18A制程PAM-4的研究論文。雖然這并不能直接證明這些公司將引入18A工藝,但至少表明了他們對這一技術(shù)的興趣和驗證意向。

在英特爾Vision 2025活動上,英特爾高級副總裁、代工部門負責(zé)人Kevin O'Buckley宣布,根據(jù)已向客戶交付的硬件來看,英特爾代工目前最為先進的Intel 18A邏輯制程已進入風(fēng)險試產(chǎn)階段。這意味著18A制程已經(jīng)技術(shù)凍結(jié),并且客戶在驗證中對該制程的表現(xiàn)感到非常滿意。英特爾下一步的目標(biāo)是實現(xiàn)18A制程的產(chǎn)能爬坡,以確保在這一節(jié)點上同時滿足技術(shù)和規(guī)模化的需求,并計劃在今年下半年實現(xiàn)最終量產(chǎn)。